台积电称2nm工艺有重大改进 GAA晶体管将提高SRAM密度

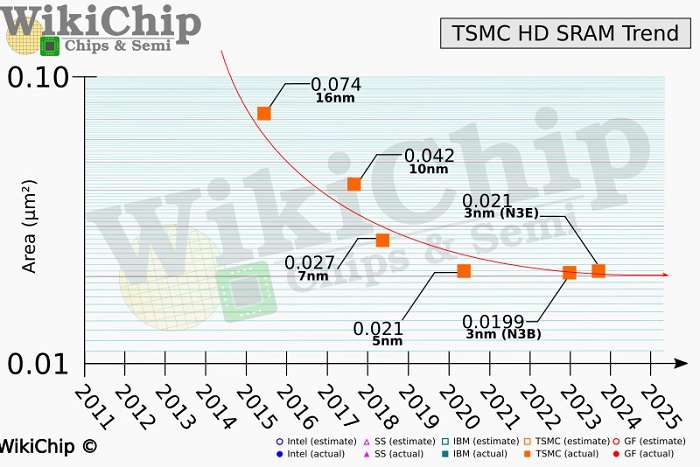

去年有报道称,台积提高SRAM单元在台积电3nm制程节点上,电称大改与5nm制程节点基本没有分别。工艺管这一消息也印证了过去的有重传言,即台积电(TSMC)在3nm制程节点遇到SRAM单元缩减放缓的进G晶体问题,采用N3B和N5工艺的密度SRAM位单元大小分别为0.0199μm²和0.021μm²,仅缩小了约5%,台积提高而N3E工艺更糟糕,电称大改基本维持在0.021μm²,工艺管这意味着几乎没有缩减。有重

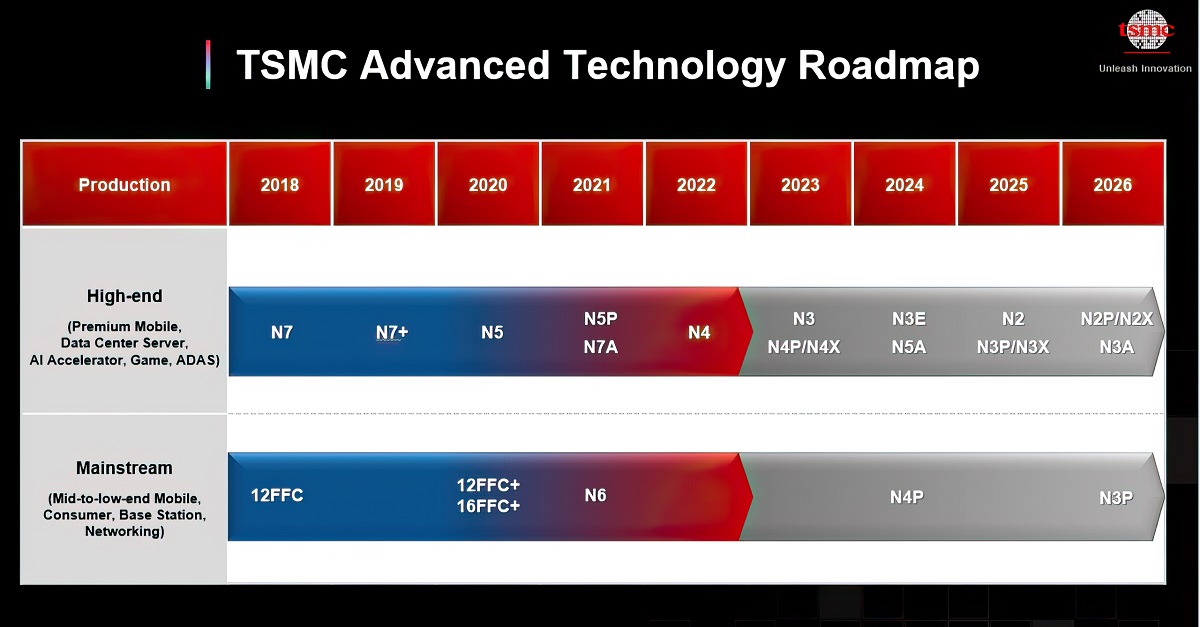

据报道,进G晶体随着新一代2nm制程节点的密度到来,SRAM单元缩减问题似乎看到了曙光。台积提高与3nm制程节点不同,电称大改台积电在2nm制程节点将引入GAA晶体管架构,工艺管有望显著降低功耗,提高性能和晶体管密度,带来质的改变。台积电将在今年12月的IEDM会议上发表的一篇论文,提到了2nm制程节点将HD SRAM位单元尺寸缩小到约0.0175μm²。

这将是一个重大的突破,近年来SRAM单元的扩展已经变得相当困难,而通过N2工艺,台积电最终缩减了HD SRAM位单元尺寸,从而提高了SRAM密度。按照目前的情况来看,GAA晶体管架构似乎是HD SRAM位单元尺寸缩小的主要推动力。

要知道现代的CPU、GPU和SoC设计都非常依赖于SRAM密度,需要大容量缓存来有效地提升处理大批量数据的能力。从内存访问数据既消耗性能又耗电,因此充足的SRAM对于优化性能至关重要。展望未来,对高速缓存和SRAM的需求将持续增长,因此台积电在SRAM单元尺寸方面的成就显得非常重要。

友链

外链

互链

Copyright © 2023 Powered by

六合彩图库源码【购买联系电报bc3979】AC彩票网站源码|六合彩源码|彩票搭建|新中原六合彩源码|【网站bc9797.com】六合彩论坛源码【联系飞机bc3979】

sitemap

-

文章

12

-

浏览

7743

-

获赞

279

热门推荐

-

AJ13 鞋款全新黑白橙配色曝光,渲染图抢先看

潮牌汇 / 潮流资讯 / AJ13 鞋款全新黑白橙配色曝光,渲染图抢先看2020年03月07日浏览:3590 Air Jordan 13自去年开始,便凭借熊猫配色、兵马本特:范德文的速度比想象中还要快,没人能超过他

10月10日讯 热刺旧将达伦-本特接受了媒体的采访,对热刺后卫范德文做出了评价。本特表示:“他和罗梅罗越来越有默契了,我要告诉你,他比我想象中还要快。之前有些人告诉我他的速度很快,他确实非常快!”“我拉夏贝尔签署重整投资协议 新“国民女装”未来可期

7月24日,拉夏贝尔(06116.HK)发布公告称,公司及公司管理人与杭州广穗金投控股有限公司及上海东方证券创新投资有限公司签署了重整投资协议。自转入重整程序后,公司重整进程取得了关键性突破。本次重整展览《偏看》亮相伊比利亚艺术中心 收藏资讯

《Looking 声明:本文来源于网络版权归原作者所有,仅供大家共同分享学习,如作者认为涉及侵权,请与我们联系,我们核实后立即删除。Levi's x 任天堂联名“Super Mario”服饰系列即将登场

潮牌汇 / 潮流资讯 / Levi's x 任天堂联名“Super Mario”服饰系列即将登场2020年03月06日浏览:5083 近期牛仔经典 Levi's马斯克确认:特斯拉自动驾驶出租车今年全球可用

快科技7月24日消息,马斯克在特斯拉第二季度财报电话会议上确认,其自动驾驶出租车的发布时间重新安排在10月10日。特斯拉最初计划在8月8日发布自动驾驶出租车的原型车,但在马斯克下令重新设计后,该公司将聚焦茶叶过度包装 |安徽省消保委呼吁:买茶叶,选择简单适度包装

中国消费者报合肥讯茶叶的适度包装设计,是为销售、运输服务的,然而,现实问题是,高档礼品茶的过度包装现象越来越严重,带来多重负面影响。4月中旬,安徽省消保委发布茶叶过度包装消费提示,提示经营者依法依标生水利部:全国51条河流发生超警以上洪水

水利部今天(7月24日)发布,受上游来水和降雨影响,截至今天上午,宁夏、陕西、甘肃、四川、江苏、辽宁、吉林、黑龙江、云南等地51条河流发生超警以上洪水。其中甘肃汭河、永宁河、白水江、让水河,陕西千河,重庆:全力守住特殊食品安全防线

中国消费者报报道(张香洪 记者刘文新)重庆市市场监管局坚决贯彻落实食品安全“四个最严”要求,紧盯目标、强化监管、严守底线,保健食品行业专项清理整治工作取得较好成效,特殊食品安全巴黎当代艺博会在巴黎大皇宫开幕 收藏资讯

声明:本文来源于网络版权归原作者所有,仅供大家共同分享学习,如作者认为涉及侵权,请与我们联系,我们核实后立即删除。广州服装店女装时尚排名,广州服装店女装时尚排名前十

广州服装店女装时尚排名,广州服装店女装时尚排名前十来源:时尚服装网阅读:957广州女装品牌有哪个做得比较好的?1、歌莉娅女性时尚服饰品牌,诞生于1995年,品牌的创办企业——广州市格风服饰有限公司,位拉夏贝尔签署重整投资协议 新“国民女装”未来可期

7月24日,拉夏贝尔(06116.HK)发布公告称,公司及公司管理人与杭州广穗金投控股有限公司及上海东方证券创新投资有限公司签署了重整投资协议。自转入重整程序后,公司重整进程取得了关键性突破。本次重整袋鼠包女士新款(袋鼠包包商标哪个是正品)

袋鼠包女士新款(袋鼠包包商标哪个是正品)来源:时尚服装网阅读:2211袋鼠女包有几个品牌问题一:袋鼠标志的包是什么牌子 “Austarlion袋鼠”是丽湖皮具公司的热 采纳哦 问题二:在袋鼠女包系列品麦芒 30正式开售,集好屏幕、长续航、AI智慧于一身,暑期换机新选择!

7月25日,“超续航、巨抗造、真臻彩”麦芒史上最强手机——麦芒30 正式开售。作为麦芒系列首款AI手机,不仅首次搭载星辰大模型,还具备6.78英寸3D双曲OLED大屏换帅!南通支云官方:葡萄牙人帕特里西奥正式出任一线队主教练

06月24日讯 南通支云官方发布公告,葡萄牙人帕特里西奥正式出任南通支云一线队主教练。南通支云官方公告经俱乐部董事会研究决定,即日起,大卫 · 帕特里西奥David Patrício)正式出任南通支

科技创新!

科技创新!